MLCC端电极制备工艺的研究分析

|

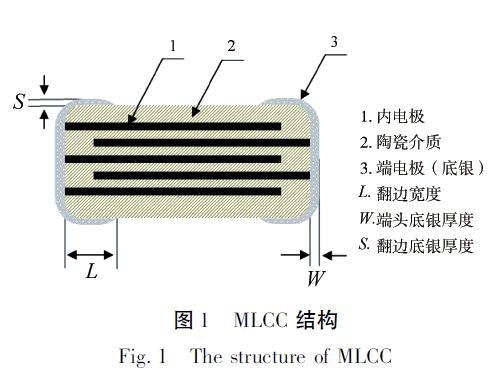

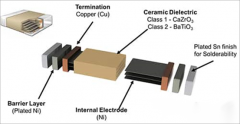

前 言 多层瓷介电容器(MLCC,Multi - Layer Ceramic Capacitors) 作为主要的基础元件之一,市场需求巨大,在军用、民用等各种电子装备中得到广泛应用,它是电子技术尤其是表面组装技术(SMT)不可缺少的电子元件之一。其中,端电极附着力导致的开路失效作为印制电路板最常见的失效类型之一,严重影响整机可靠性。本文从MLCC制备工艺环节中的封端和烧端工艺入手,试验分析了产品翻边宽度、底银层厚度、烧端峰值温度、烧端峰值温度保温时间以及烧端装载密度对端电极附着力的影响。 文章内容 1、样品制备 使用多层瓷介电容未封端芯片,采用纯银可镀端浆,调整控制封端参数,制备得到不同翻边宽度、不同底银层厚度的试验样品(图1); 通过调节设备烧端峰值温度和带速,制备得到不同烧端峰值温度和峰值温度保温时间的试验样品;通过承烧板装载数目不等的待烧端芯片,制备得到不同烧端装载密度的试验样品。

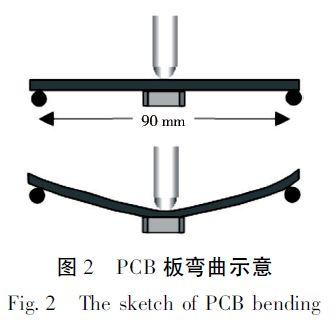

2、测试方法 (1)破坏性物理分析 按照GJB 4027A-2006方法0202进行试验评估。过程使用全自动金相抛磨机进行制样,使用金相显微镜进行样品观察分析。 (2)端面结合强度 按照GB 2693-90 第4.35条试验。每组样品抽样8只,样品采用回流焊接方式安装至PCB板上,试验时采用电容器朝下的方式将PCB板置于弯曲夹具中,下压探头以1mm/s的速率下降(见图2)。下压探头每下降1mm测试记录产品容量,直至产品容量下降超过初始容量10%即判定失效并停止试验。

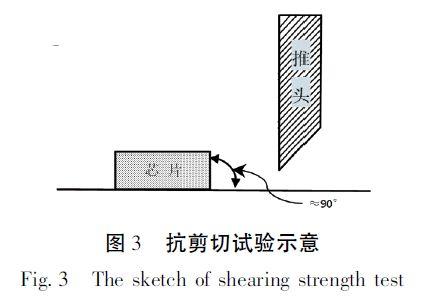

(3)抗剪切强度 按照GJB 548B-2005方法2019.2试验。每组样品抽样10只,样品采用回流焊接方式安装至PCB 板上,采用MFM1200型拉力剪切力测试仪对样品进行破坏性试验,试验过程中芯片以0.1mm/s速率水平驶向推头,直至样品从基板脱落,试验后统计其抗剪切力数值,试验方法示意如图3。

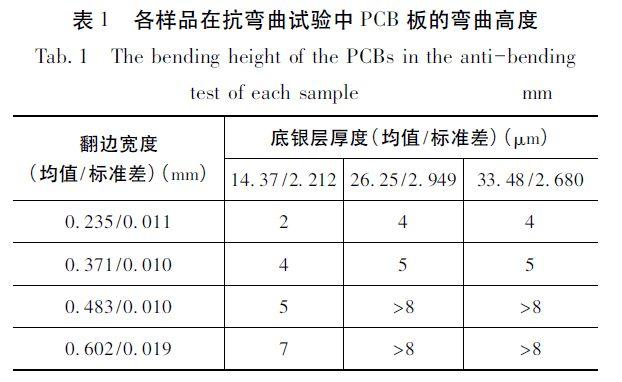

结果分析 1、封端工艺影响 封端过程即是在一定的工艺参数条件下,在经烧结处理后的芯片端头制备一定翻边宽度和底银层厚度的端电极,以实现端电极和内电极的导通。封端工艺主要是产品翻边宽度和底银层厚度对产品外观、尺寸和性能产生影响。 (1)端面结合强度试验 不同翻边宽度和底银层厚度产品其端面结合强度试验结果见表1。

表1结果显示,随着翻边宽度和底银层厚度的增加,产品端电极的抗弯曲性能得到明显提升。分析认为,在PCB基板受到外力弯曲变形时,端电极翻边在杠杆效应下,翻边宽度越宽此时作用于产品瓷体上的力相对越小,同时翻边宽度越宽可为端电极提供的抓附面积越大,可减少单位瓷体面积的受力强度,避免应力集中; 端电极附着力很大程度依靠端浆中玻璃料实现,底银层厚度越厚含有的玻璃料越多,可为端电极提供更大的附着力。 因此,具备较宽翻边宽度和较厚底银层厚度的产品可承受PCB基板更大的形变量。

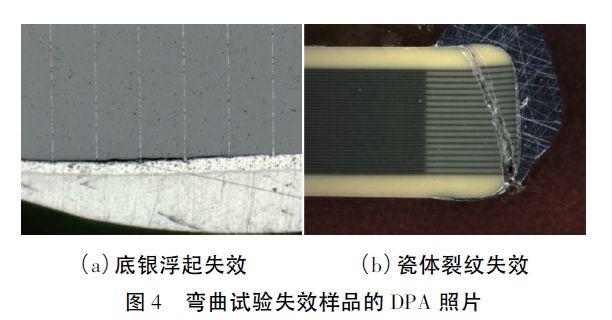

MLCC的失效机理和失效原因很多,单一失效模式可能对应着多种的失效机理和原因。采用热风枪对失效产品解焊并进行DPA分析,结果显示,底银层厚度为14. 37μm 时4种不同翻边宽度制备的产品均存在一定比例的底银浮起缺陷(图4(a)),其余组别产品失效表征均始于翻边的45°角瓷体裂纹(图4(b))。 分析认为,14. 37μm底银层厚度产品,其端头底银玻璃料总含量偏低,在烧端时玻璃料向瓷体渗入量不足,导致产品底银浮起致使失效 ;当底银层厚度≥26.25μm,底银中玻璃料总含量较为充裕,在基板极限弯曲状态下底银附着力仍具有较大的富余量,此时瓷体发生脆性变形导致产品失效。 (2)抗剪切强度试验 抗剪切强度试验对于端电极附着力具有一定的“量化”参考意义,并可根据失效状态识别产品机械性能方面的薄弱点。各组产品失效时的平均抗剪切力数据见表2。 |