总结:去耦电容的有效使用方法

|

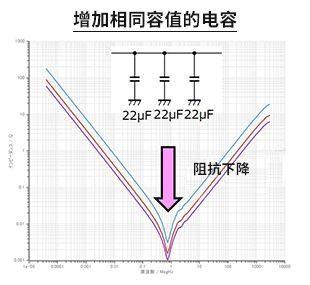

去耦电容有效使用方法的要点大致可以分为以下两种。另外,还有其他几点需要注意。 使用多个容值相同的电容时 右图是使用1个22F的电容时(蓝色)、增加1个变为2个时(红色)、再增加1个变为3个(紫色)时的频率特性。 如图所示,当增加容值相同的电容后,阻抗在整个频率范围均向低的方向转变,也就是说阻抗越来越低。 这一点可通过思考并联连接容值相同的电容时,到谐振点的容性特性、取决于ESR(等效串联电阻)的谐振点阻抗、谐振点以后的ESL(等效串联电感)影响的感性特性来理解。 并联的电容容值是相加的,所以3个电容为66F,容性区域的阻抗下降。

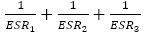

谐振点的阻抗是3个电容的ESR并联,因此为

谐振点以后的感性区域的ESL也是并联,因此为

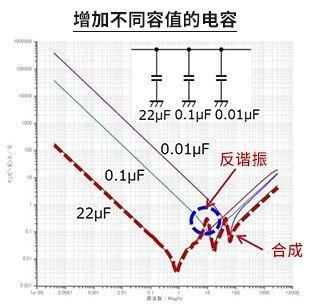

由此可知,通过使用多个相同容值的电容,可在整个频率范围降低阻抗,因此可进一步降低噪声。 使用多个容值不同的电容时 这些曲线是在22F的电容基础上并联增加0.1F、以及0.01F的电容后的频率特性。 通过增加容值更小的电容,可降低高频段的阻抗。相对于一个22F电容的频率特性来说,0.1F和0.01F的特性是合成后的特性(红色虚线)。 这里必须注意的是,有些频率点产生反谐振,阻抗反而增高,EMI恶化。反谐振发生于容性特性和感性特性的交叉点。

所增加电容的电容量,一般需要根据目标降噪频率进行选型。 另外,在这里给出的频率特性波形图是理想的波形图,并未考虑PCB板的布局布线等引起的寄生分量。在实际的噪声对策中,需要考虑寄生分量的影响。

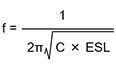

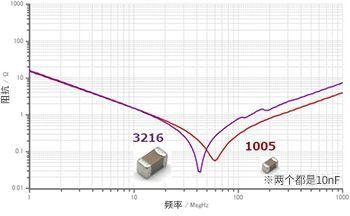

即使容值相同也要使用尺寸较小的电容 对于积层陶瓷电容(MLCC),有时会准备容值相同但尺寸不同的几个封装。ESL取决于引脚部位的结构。尺寸较小的电容基本上引脚部位也较小,通常ESL较小。 右图是容值相同、大小不同的电容的频率特性示例。如图所示,更小的1005尺寸的谐振频率更高,在之后感性区域的频率范围阻抗较低。这正如在“电容的频率特性”中所介绍的,电容的谐振频率是基于以下公式的,从公式中可见,只要容值相同,ESL越低谐振频率越高。另外,感性区域的阻抗特性取决于ESL,这一点也曾介绍过。

关于噪声对策,当需要降低更高频段的噪声时,可以选择尺寸小的电容。 使用旨在降低ESL的电容 |