MLCC电容为什么要靠近电源引脚

时间:2023-08-09来源:佚名

|

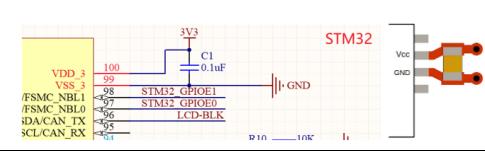

在硬件设计中,不论是电源芯片还是单片机芯片,有经验的工程师通常会在其周围放置一两个MLCC电容,通常采用100nF 10nF的电容组合,并紧密靠近芯片的电源引脚。

这样的做法可以改善电源纹波。关于这一点,一般的结论是,陶瓷电容距离芯片引脚越近,去耦效果越好,对滤除高频噪声也越有效。相比之下,将电解电容放置靠近芯片引脚效果不明显。对于“去耦半径”的术语,有些显得高深:当芯片对电流需求发生变化时,会在电源平面的一个非常局部的区域内产生电压扰动,电容必须补偿这一电流(或电压),因此必须先感知到这个电压扰动。电容能感知最大距离的电流/电压扰动的能力被称为去耦半径。这是根据资料找到的解释,尽管看过之后仍有些难以理解。因此,为了说明MLCC电容靠近或远离电源芯片引脚的影响有多大,我将通过实验来说明。 这种紧贴芯片引脚的电容称为退藕电容,与之对应的是耦合电容(couple cap)。退藕电容的名字可以理解为,它去除了不需要的耦合信号。我们可以通过仿真来观察电容对电源电压的影响。

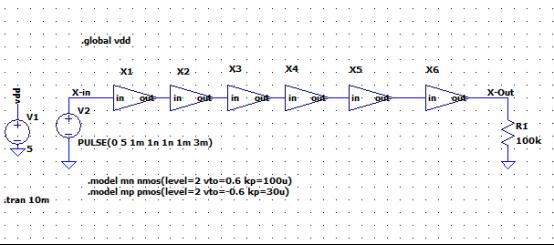

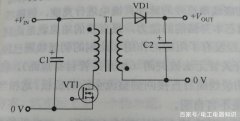

我进行了以下四个仿真测试实验:驱动信号控制反相器不停地翻转,接一个100K的负载,基本上产生了很小的电流,这种情况基本上相当于轻负载。在这种负载影响下,电源是否出现电压波动呢? 在仿真参数设计中,电源到反相器X1-X6的走线具有10nF的寄生电感和10mΩ的走线阻抗。使用的电容和电感模型均由仿真软件提供。当没有加电容时测量的结果显示,Vdd电源电压的最大和最小值在5.5V到4.7V之间,Vpp=0.7V。 |