电源完整性的去耦和层间耦合电容

|

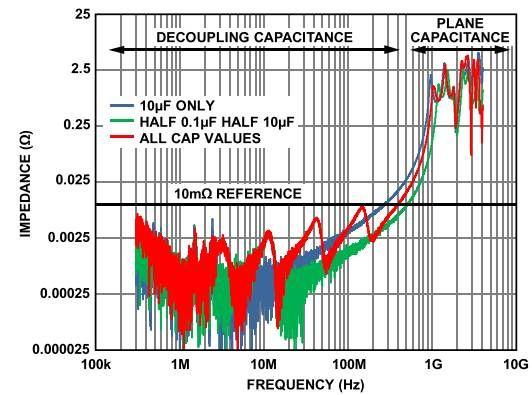

在电子产品设计中,我们在追求产品功能以及成本的优化时,往往我们会忽略使用去耦的目的,仅仅知道在电路板上分散大小不同的许多电容,使较低阻抗电源连接到地。但问题依旧:需要多少电容?许多相关文献表明,必须使用大小不同的许多电容来降低功率传输系统(PDS)的阻抗,但这并不完全正确。相反,仅需选择正确大小和正确种类的电容就能降低PDS阻抗。 举个例子 考虑设计一个10 mΩ参考层,如图1所示。如红色曲线所示,系统电路板上使用许多不同值的电容,0.001 μF、0.01 μF、0.1 μF等等。这当然可以降低500 MHz频率范围内的阻抗,但是,请看绿色曲线,同样的设计仅使用0.1 μF和10 μF电容。这证明,如果使用正确的电容,则不需要如此多的电容。这也有助于节省空间和物料(BOM)成本。

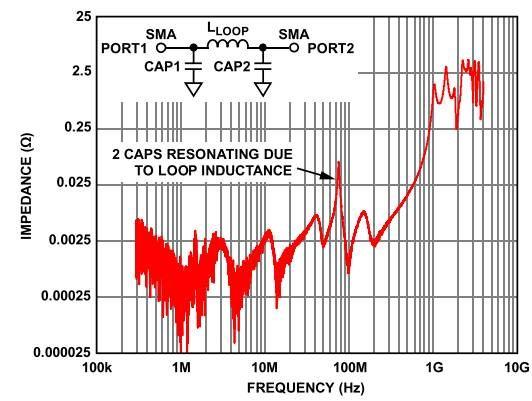

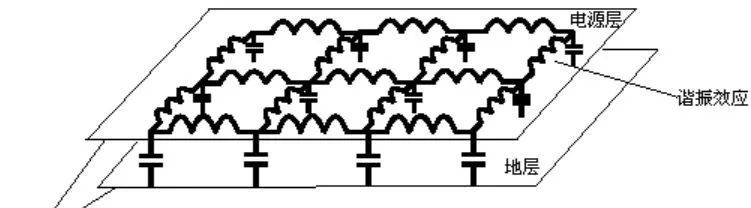

图1. 电容示例 注意,并非所有电容“生而平等”,即使同一供应商,工艺、尺寸和样式也有差别。如果未使用正确的电容,不论是多个电容还是几个不同类型,都会给PDS带来反作用。结果可能是形成电感环路。电容放置不当或者使用不同工艺和型号的电容(因而对系统内的频率做出不同响应),彼此之间可能会发生谐振,见图2。

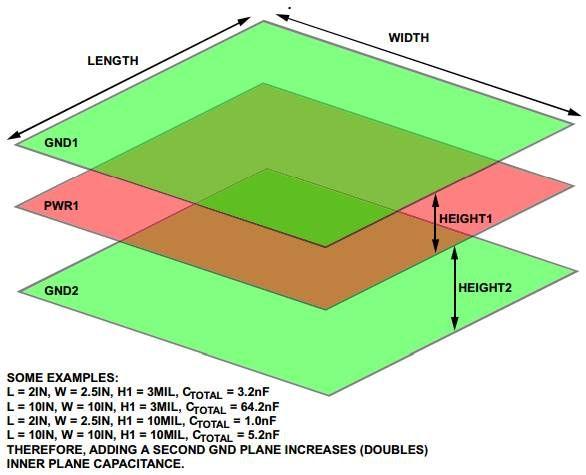

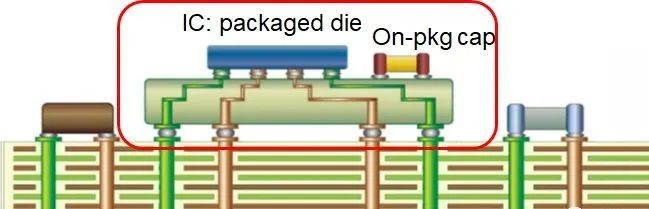

图2. 谐振电容 所以,了解系统所用电容类型的频率响应很重要。随便选用电容,会让设计低阻抗PDS系统的努力付之东流。如何设计出合格的PDS要设计出合格的PDS,需要使用各种电容(见图1)。PCB上使用的典型电容值只能将直流或接近直流频率至约500 MHz范围的阻抗降低。高于500 MHz频率时,电容取决于PCB形成的内部电容。注意,电源层和接地层紧密叠置会有帮助。 应当设计一个支持较大层电容的PCB层叠结构。例如,六层堆叠可能包含顶部信号层、第一接地层、第一电源层、第二电源层、第二接地层和底部信号层。规定第一接地层和第一电源层在层叠结构中彼此靠近,这两层间距为2到4密尔,形成一个固有高频层电容。此电容的最大优点是它是免费的,只需在PCB制造笔记中注明。如果必须分割电源层,同一层上有多个VDD电源轨,则应使用尽可能大的电源层。不要留下空洞,同时应注意敏感电路。这将使该VDD层的电容最大。 如果设计允许存在额外的层(上例中,从六层变为八层),则应将两个额外的接地层放在第一和第二电源层之间。在核心间距同样为2到3密尔的情况下,此时层叠结构的固有电容将加倍,示例见图3。

图3. 高频层电容示例 与添加更多分立高频电容以在高频时保持低阻抗相比,此结构更易于设计。 PDS的任务是将响应电源电流需求而产生的电压纹波降至最低,这点很重要但常被忽略。所有电路都需要电流,有些电路需求量较大,有些电路则需要以较快的速率提供电流。采用充分去耦的低阻抗电源层或接地层以及良好的PCB层叠,有助于将因电路的电流需求而产生的电压纹波降至最低。例如,根据所用的去耦策略,如果系统设计的开关电流为1A,PDS的阻抗为10 mΩ,则最大电压纹波为10 mV。计算很简单:V = IR。 凭借完美的PCB堆叠,可覆盖高频范围,同时在电源层起始入口点和高功率或浪涌电流器件周围使用传统去耦,可覆盖低频范围(<500 MHz)。这可确保PDS阻抗在整个频率范围内均最低。没有必要各处都配置电容;电容正对着每个IC放置会破坏许多制造规则。如果需要这种严厉的措施,则说明电路存在其它问题。Got it? 在高度集成的电子产品中,电源系统的设计占到了设计工作量的50%左右;对于复杂的FPGA类型的产品应用,在电路中常常会达到15~30路不同的电源。电源完整性的目的就是给系统提供持续、稳定、干净的电源,保证系统稳定的工作。在数字系统中,使信号完整性满足系统设计的要求也需要有一个非常稳定的电源系统,但是又不能使电源系统超标。所以在设计电源完整性时,不仅仅关注的是去耦电容,还需要关注电源完整性、信号完整性和电磁兼容性这个“生态系统”,尤其是要考虑高度集成化的数字电路对电源完整性的影响… …但是传统分析信号完整性和电源完整性都是分开分析的,为了更好的分析SI和PI的相互影响,我们需要把SI和PI放在同一个EM仿真中来分析。

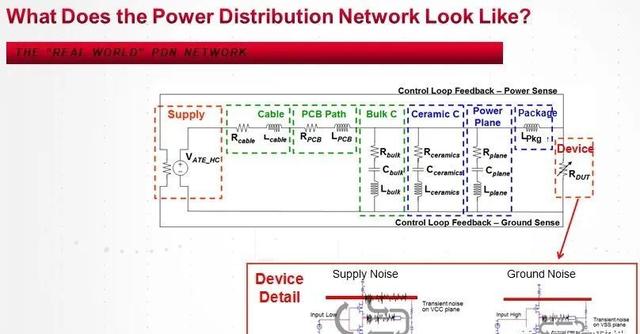

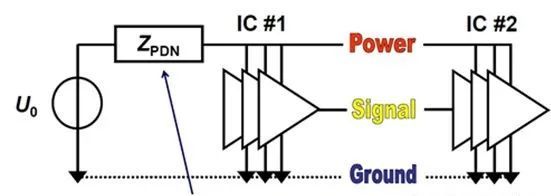

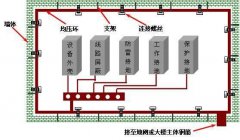

PDN 真实的PDN是什么样子的呢?主要分为三个部分:供电端(VRM)、用电端(Sink)和传输通道(PCB、Cable、瓷片电容等等)。

电路板设计中,都有电源分配网络系统。电源分配网络系统的作用就是给系统内所有器件或芯片提供足够的电源,并满足系统对电源稳定性的要求。 我们看到电源、GND网络,其实分布着阻抗。

电源噪声余量计算: 1、芯片的datasheet会给一个规范值,通常是5%;要考虑到稳压芯片直流输出误差,一般是 /_2.5%,因此电源噪声峰值幅度不超过 /_2.5%。 2、如芯片的工作电压范围是3.13~3.47,稳压芯片标出输出电压是3.3V,安装在电路板后的输出电压是3.36V。容许的电压的变化范围是3.47-3.36=110mv。稳压芯片输出精度是 /_1%,及3.36* /_1%= /_33.6mv。电源噪声余量为110-33.6=76.4mv。 计算电源噪声要注意五点 (1)稳压芯片的输出的精确值是多少。 (2)工作环境的是否是稳压芯片所推荐的环境。 (3)负载情况是怎么样,这对稳压芯片输出也有影响。 (4)电源噪声最终会影响到信号质量。而信号上的噪声来源不仅仅是电源噪声,反射窜扰等信号完整性问题也会在信号上叠加,因此不能把所有噪声余量留给电源系统。 (5)不同的电压等级对电源噪声要求也不样,电压越小噪声余量越小。模拟电路对电源要求更高。 电源噪声来源 (1)稳压芯片输出的电压不是恒定的,会有一定的纹波。 (2)稳压电源无法实时响应负载对于电流需求的快速变化。稳压电源响应的频率一般在200Khz以内,能做正确的响应,超过了这个频率则在电源的输出短引脚处出现电压跌落。 (3)负载瞬态电流在电源路径阻抗和地路径阻抗产生的压降。 (4)外部的干扰。 目标阻抗 目标阻抗是电源系统的瞬态阻抗,对快速变化的电流的表现出来的一种特性阻抗。目标阻抗和一定宽度的频率有关,在感兴趣的频率范围内,电源阻抗都不能超过这个值。 |