常见的外围硬件电路设计参考及注意事项

|

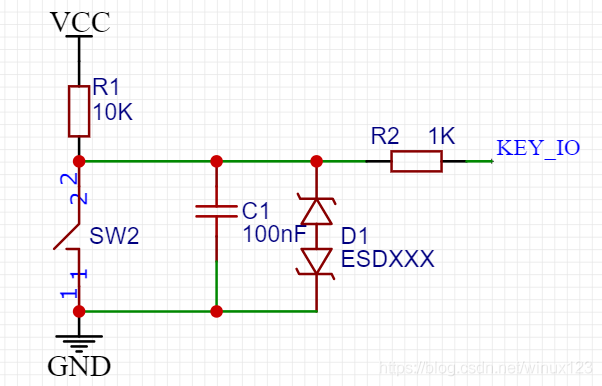

从事嵌入式这个行业已经有七八年了,在此我给大家分享分享一些硬件电路的设计方案和心得,供一些刚学嵌入式的朋友参考,大神和老鸟请忽略哈。还有,因为本人知识非常有限,也不是专门做电路设计的,如果有什么错漏的地方非常欢迎大家指正,请大家轻喷轻喷,多多包涵。 一、按键电路的常用设计参考

1、R1上拉电阻 将不确定的信号通过一个电阻钳位在高电平,维持在不被触发的状态或是触发后回到原状态。(个人建议加上) 2、C1电容 减小按键抖动及高频信号干扰。(个人建议加上) 3、R2限流电阻(取值100欧~10k不等,如果有设置内部上拉,该值不能太大,否则电流不足以拉低IO口) 保护IO口 防止过流过高电压烧坏IO口,对静电或者一些高压脉冲有吸收作用。(个人建议加上) 4、D1 ESD二极管 静电保护二极管,防止静电干扰或者损坏IO口。(这个根据PCB的成本及防护级别要求来决定添加与否) 二、外接信号输入设计参考(和按键有点类似)

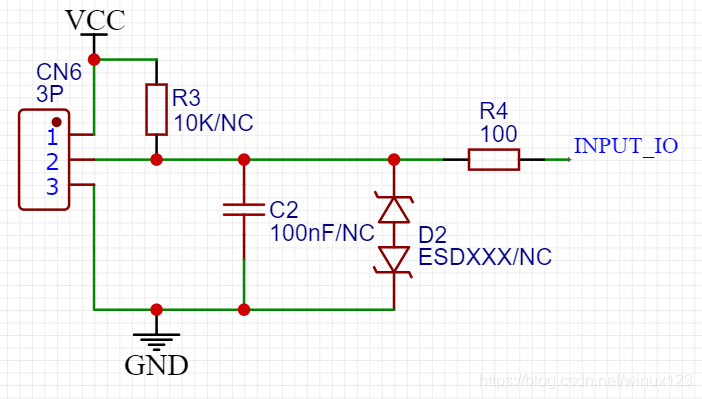

1、R3上拉电阻 将不确定的信号通过一个电阻钳位在高电平,维持在不被触发的状态或是触发后回到原状态。(如果外接的连接线比较长,芯片内部上拉能力比较弱,则建议加上。平时通信距离不长,有内部上拉则可以省略) 2、C2电容 防止高频信号干扰。(注意,如果输入频率信号比较大,C2容值要对应减少,或者直接省略C2) 3、R4限流电阻 保护IO口 防止过流过高电压烧坏IO口,对静电或者一些高压脉冲有吸收作用。(个人建议加上) 4、D2 ESD二极管 静电保护二极管,防止静电干扰或者损坏IO口。(这个根据PCB的成本及防护级别要求来决定添加与否) 三、输出电路继电器设计参考

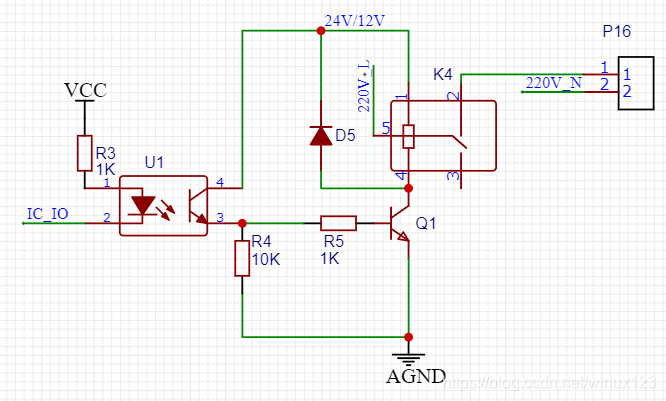

1、U1光耦 分离高低压,防止高压干扰,实现电气隔离 2、D5 1N4148 续流二极管 bai保护元件不被感应电压击du穿或烧坏,以并联的方式接到产生感应电动势的元件两端,并与其形成回路,使其产生的高电动势在回路以续电流方式消耗,从而起到保护电路中的元件不被损坏的作用。 四、达林顿晶体管设计参考应用 |